# **RoHS Compliant**

# Micro SATA Disk Chip

μSDC-M Plus Specifications

**November 6, 2015**

Version 1.0

#### Apacer Technology Inc.

1F, No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City, Taiwan, R.O.C Tel: +886-2-2267-8000 Fax: +886-2-2267-2261 www.apacer.com

# **Features:**

#### • Standard Serial ATA Interface

- SATA 6.0 Gbps interface compliance

- ATA-compatible command set

#### Capacities

- MLC: 8, 16, 32, 64, 128 GB

- SLC-Lite: 8, 16, 32, 64 GB

#### Performance\*

- Sustained read: up to 510 MB/sec

- Sustained write: up to 180 MB/sec

#### • Flash Management

- Supports ECC up to 72 bit correction per 1K Byte data

- Wear leveling

- Flash bad-block management

- S.M.A.R.T.

- Power Failure Management

- ATA Secure Erase

- TRIM

- NAND Flash Type: MLC & SLC-Lite

#### Temperature Ranges

Operating

Standard: 0°C to 70°C Extended: -40°C to 85°C

- Storage: -40°C to 85°C

#### Supply Voltage

- $-3.3V \pm 5\%$

- $-1.8V \pm 5\%$

- $-1.2V \pm 5\%$

#### Power Consumption (typical)\*

- Active mode: 445 mA

- Idle mode: 90 mA

#### SATA Power Management

- Partial mode

- Slumber mode

- Device Sleep mode

#### Package

- 16 x 20 x 1.4, unit : mm

- 156 Ball

#### Form Factor

JEDEC MO-276

RoHS Compliant

<sup>\*</sup>Varies from capacities. The values for performances and power consumptions presented are typical and may vary depending on flash configurations or platform settings.

# **Table of Contents**

| 1. GENERAL DESCRIPTION                                                                                                                                                                               | 3  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. PIN ASSIGNMENTS                                                                                                                                                                                   | 3  |

| 3. PRODUCT SPECIFICATIONS                                                                                                                                                                            | 8  |

| 3.1 CAPACITY                                                                                                                                                                                         | 9  |

| 4. FLASH MANAGEMENT                                                                                                                                                                                  |    |

| 4.1 ERROR CORRECTION/DETECTION 4.2 FLASH BLOCK MANAGEMENT 4.3 WEAR LEVELING 4.4 POWER FAILURE MANAGEMENT 4.5 ATA SECURE ERASE 4.6 S.M.A R.T 4.7 TRIM 4.8 SATA POWER MANAGEMENT 5. SOFTWARE INTERFACE |    |

| 5.1 COMMAND SET                                                                                                                                                                                      |    |

| 6. ELECTRICAL SPECIFICATION                                                                                                                                                                          | 13 |

| 6.1 OPERATING VOLTAGE                                                                                                                                                                                | 13 |

| 7. MECHANICAL SPECIFICATIONS                                                                                                                                                                         |    |

| 8. PRODUCT ORDERING INFORMATION                                                                                                                                                                      |    |

| 8.1 PRODUCT CODE DESIGNATION                                                                                                                                                                         |    |

# 1. General Description

Apacer Micro SDC (Micro SATA Disk Chip,  $\mu$ SDC) presents a revolutionary breakthrough of NAND flash storage technology. This micro sized SSD delivers all the technological benefits in NAND based storage solution with ultra speed SATA 6.0 Gbps interface in an embedded BGA form factor, compatible with JEDEC MO-276. Formed in a size of an IC chip, the speedy  $\mu$ SDC can offer up to 64GB in capacity and the performance level can reach up to 510 MB/s for read and 180 MB/s for write. With its micro-size and ultra speed, the  $\mu$ SDC is definitely the ideal storage solution for high performance demand mobile devices.

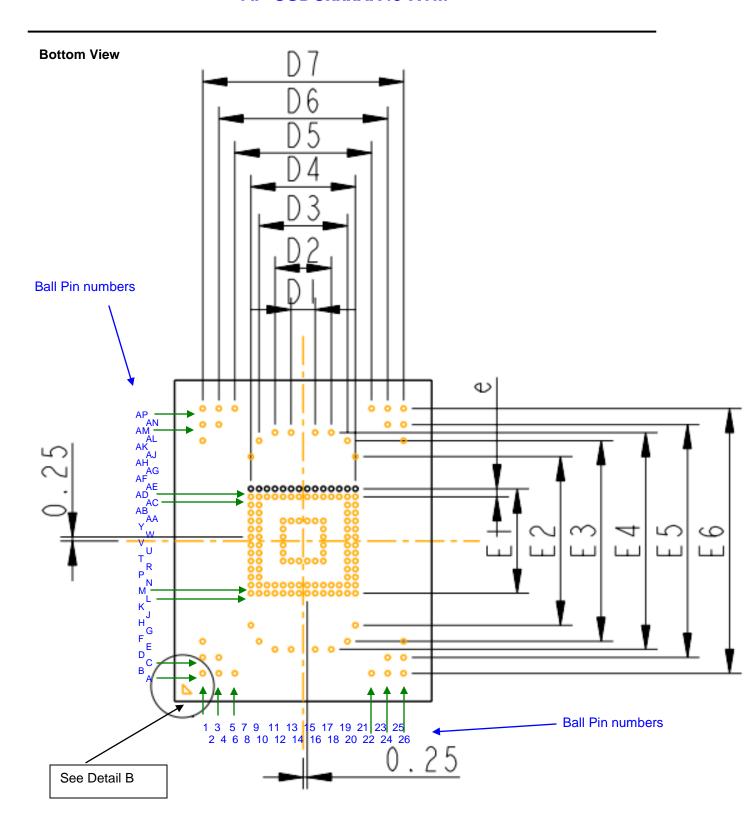

# 2. Pin Assignments

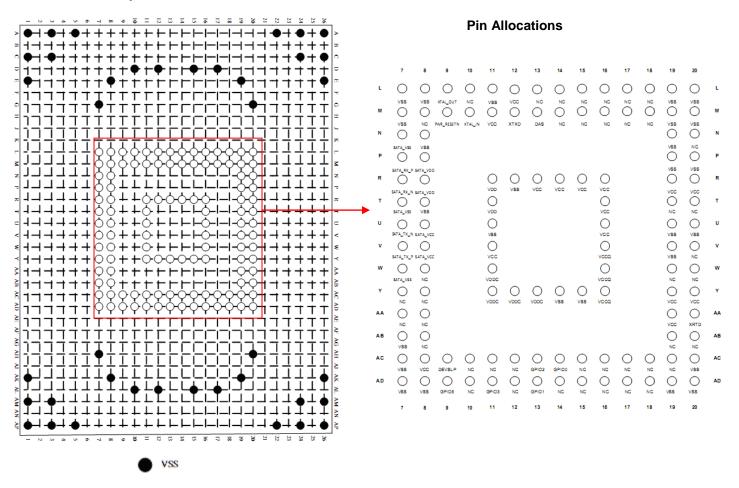

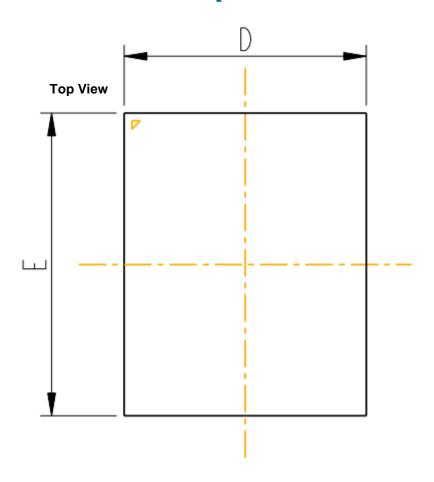

#### **Top View**

## Top View (enlarged image)

## Pin Allocations (enlarged image)

|    | 7         | 8             | 9          | 10      | 11       | 12      | 13      | 14      | 15      | 16      | 17      | 18      | 19         | 20       |    |

|----|-----------|---------------|------------|---------|----------|---------|---------|---------|---------|---------|---------|---------|------------|----------|----|

|    |           |               |            |         | _        |         |         |         |         |         | _       |         |            |          |    |

| L  | $\circ$   | $\circ$       | $\circ$    | $\circ$ | $\circ$  | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$    | $\circ$  | L  |

| м  | VSS       | VSS           | XTAL_GUT   | NC      | vss      | VCC     | NC      | NC      | NC      | NC      | NC      | NC      | VSS        | VSS      | м  |

|    | vss       | $\overline{}$ | PWR_RESETN | XTAL_IN | voc      | XTXD    | DAS     | NC      | NC      | NC      | NC      | NC      | vss        | vss      |    |

| N  | $\circ$   | $\circ$       |            |         |          |         |         |         |         |         |         |         | $\circ$    | $\circ$  | N  |

| Р  | SATA_VSS  | vss           |            |         |          |         |         |         |         |         |         |         | VSS        | NC       | Р  |

| -  | $\circ$   | $\circ$       |            |         |          |         |         |         |         |         |         |         | _          | _        | -  |

| R  | SATA_RX_P | SATA_VDD      |            |         | 0        | 0       | 0       | 0       | 0       | 0       |         |         | O VSS      | VSS      | R  |

|    | SATA_RX_N | SATA_VDD      |            |         | VDD      | VSS     | VCC     | VCC     | VCC     | vcc     |         |         | vcc        | vcc      |    |

| т  | $\circ$   | $\circ$       |            |         | 0        |         |         |         |         | $\circ$ |         |         | $\circ$    | $\circ$  | т  |

|    | SATA_VSS  | vss           |            |         | VDD      |         |         |         |         | vcc     |         |         | NC         | NC       |    |

| U  | SATA_TX_N | 0             |            |         | O<br>vss |         |         |         |         | VCC     |         |         | O<br>vss   | O<br>vss | U  |

| v  |           |               |            |         | 0        |         |         |         |         | $\cap$  |         |         | $\bigcirc$ | Õ        | v  |

|    | SATA_TX_P | SATA_VCC      |            |         | vcc      |         |         |         |         | vccq    |         |         | vss        | NC       |    |

| w  | 0         | $\circ$       |            |         | $\circ$  |         |         |         |         | 0       |         |         | $\circ$    | $\circ$  | w  |

|    | SATA_VSS  | NC            |            |         | VDDC     | _       | _       | _       | _       | VCCQ    |         |         | NC         | NC       |    |

| Υ  | $\circ$   | $\circ$       |            |         | 0        | 0       | $\circ$ | 0       | $\circ$ | 0       |         |         | $\circ$    | $\circ$  | Υ  |

|    | NC        | NC            |            |         | VDDC     | VDDC    | VDDC    | VSS     | VSS     | VCCQ    |         |         | VCC        | VCC      |    |

| AA | NC        | O<br>NC       |            |         |          |         |         |         |         |         |         |         | VCC        | XRTD     | AA |

| АВ | 0         | 0             |            |         |          |         |         |         |         |         |         |         | 0          | 0        | AB |

|    | vss       | NC            |            |         |          |         |         |         |         |         |         |         | NC         | NC       |    |

| AC | $\circ$   | $\circ$       | $\circ$    | $\circ$ | $\circ$  | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$    | $\circ$  | AC |

|    | vss       | vcc           | DEVSLP     | NC      | NC       | NC      | GPI02   | GPI00   | NC      | NC      | NC      | NC      | NC         | vss      |    |

| AD | VSS       | 0             | O          | 0       | O        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0          | 0        | AD |

|    | vss       | VSS           | GPI06      | NC      | GPIO3    | NC      | GPI01   | NC      | NC      | NC      | NC      | NC      | VSS        | VSS      |    |

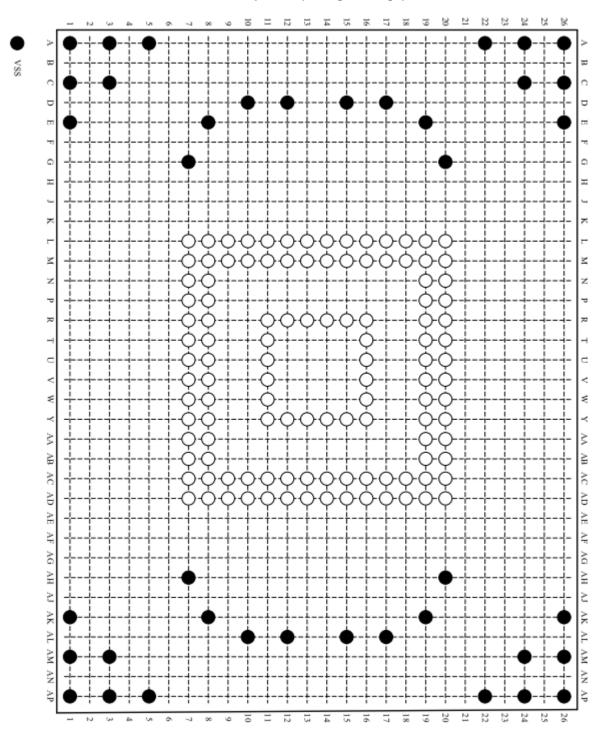

## **Pin Description**

| Name<br>(Bottom view)  | BGA156                                                                                                                                                                       | Type<br>(I/O) | Description                                                               |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------|

| (Bottom view)          | (Top view)                                                                                                                                                                   | ART/GPIO      |                                                                           |

| XTXD                   | M12                                                                                                                                                                          | O             |                                                                           |

| XRXD                   | AA20                                                                                                                                                                         | Ĭ             | UART transmit/receive port (For Apacer internal debug use)                |

| GPIO0*                 | AC14                                                                                                                                                                         | '             | ( compared members are agree)                                             |

| GPIO1*                 | AD13                                                                                                                                                                         |               |                                                                           |

| GPIO2*                 | AC13                                                                                                                                                                         | 10            | General purpose input/output pins                                         |

| GPIO3*                 | AD11                                                                                                                                                                         |               |                                                                           |

| GPIO6*                 | AD9                                                                                                                                                                          |               |                                                                           |

| SATA_RX_N<br>SATA_RX_P | R7<br>P7                                                                                                                                                                     | ı             | Differential signal pair A. SATA device receive signal differential pair  |

| SATA_TX_N<br>SATA_TX_P | U7<br>V7                                                                                                                                                                     | 0             | Differential signal pair B. SATA device transmit signal differential pair |

| DAS                    | M13                                                                                                                                                                          | 0             | Device activity signal                                                    |

| SATA_VCC               | U8, V8                                                                                                                                                                       |               | +3.3V                                                                     |

| SATA_VDD               | P8, R8                                                                                                                                                                       |               | +1.2V                                                                     |

| SATA_VSS               | N7, T7, W7                                                                                                                                                                   |               | Ground                                                                    |

|                        |                                                                                                                                                                              | ntrol Signa   | als                                                                       |

| XTAL_IN<br>XTAL_OUT    | M10<br>L9                                                                                                                                                                    | 0<br>0        | Crystal input/output pin (40MHz)                                          |

| PWR_RESETN             | M9                                                                                                                                                                           | I             | Hardware reset, low active                                                |

|                        | Power                                                                                                                                                                        | Supply Si     | gnals                                                                     |

| VCC                    | L12, M11, R13,<br>R14, R15, R16,<br>R19, R20, T16,<br>U16, V11, Y19,<br>Y20, AA19, AC8                                                                                       |               | +3.3V                                                                     |

| VDDC                   | W11, Y11, Y12,<br>Y13                                                                                                                                                        |               | +1.2V                                                                     |

| VCCQ                   | V16, W16, Y16                                                                                                                                                                |               | +1.8V                                                                     |

| VDD                    | R11, T11                                                                                                                                                                     |               | +1.2V for PLL                                                             |

|                        |                                                                                                                                                                              | ND Signal     | S                                                                         |

| VSS                    | R12, U11, L7, L8,<br>M7, L11, L19, L20,<br>M19, M20, N19,<br>P19, AC20, AD20,<br>AD19, AD8, T8,<br>Y14, Y15, U19,<br>P20, U20, V19,<br>AC7, AB7, N8, A1,<br>C1, E1, AK1, AM1 |               | Ground                                                                    |

| VSS                    | AP1, A3, C3,<br>AM3, AP3, A5,                                                                                                                                                |               | Ground                                                                    |

|        | AP5, G7, AH7, E8,<br>AK8, D10, AL10,<br>D12, AL12, D15,<br>AL15, D17, AL17,<br>E19, AK19, G20,<br>AH20, A22, AP22,<br>A24, C24, AM24,<br>AP24, A26, C26,                                                                                    |            |                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------|

|        | E26, AK26, AM26,<br>AP26                                                                                                                                                                                                                    |            |                                                                                                    |

|        | Ot                                                                                                                                                                                                                                          | her Signal | S                                                                                                  |

| DEVSLP | AC9                                                                                                                                                                                                                                         | ļ          | Device Sleep                                                                                       |

| NC     | AA7, AB19, AB20,<br>AB8, AC10, AC11,<br>AC15, AC16,<br>AC17, AC18,<br>AC19, AD10,<br>AD12, AD14,<br>AD15, AD16,<br>AD17, AD18, L10,<br>M16, M17, M8,<br>T19, T20, W19,<br>W8, Y7, Y8, L13,<br>L14, M14, M15,<br>M18, N20, V20,<br>W20, AC12 |            | DNU                                                                                                |

| DEBUG  | L15, L16, L17,<br>L18, AA8, AD7                                                                                                                                                                                                             |            | For Apacer internal debug use<br>(AD7- Standard definition : VSS<br>Apacer definition : for dubug) |

<sup>\*</sup>The GPIO pins are non-connected by default. For specific configurations for the GPIO pins, such as Apacer Security Features, please consult with Apacer product managers or sales representatives for further details.

# 3. Product Specifications

## 3.1 Capacity

Table 3-1: Capacity Specifications

| Capacity | Total bytes*    | Cylinders | Heads | Sectors | Max LBA     |

|----------|-----------------|-----------|-------|---------|-------------|

| 8 GB     | 8,012,390,400   | 15,525    | 16    | 63      | 15,649,200  |

| 16 GB    | 16,013,942,784  | 16,383    | 16    | 63      | 31,277,232  |

| 32 GB    | 32,017,047,552  | 16,383    | 16    | 63      | 62,533,296  |

| 64 GB    | 64,023,257,088  | 16,383    | 16    | 63      | 125,045,424 |

| 128 GB   | 128,035,676,160 | 16,383    | 16    | 63      | 250,069,680 |

<sup>\*</sup>Display of total bytes varies from file systems.

LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the lifespan of the device. However, the total usable capacity of the SSD is most likely to be less than the total physical capacity because a small portion of the capacity is reserved for device maintenance usages.

#### 3.2 Performance

#### 3.2.1 MLC

Table 3-2: MLC Performance

| Capacity Performance   | 8 GB | 16 GB | 32 GB | 64 GB | 128 GB |

|------------------------|------|-------|-------|-------|--------|

| Sustained read (MB/s)  | 140  | 245   | 420   | 450   | 495    |

| Sustained write (MB/s) | 105  | 170   | 155   | 165   | 175    |

| Note:                  |      |       |       |       |        |

Note:

Results may differ from various flash configurations or host system settings.

IOPS results were measured on 8GB span (16777216 sectors Disk Size), 32 Outstanding I/Os (QD=32), Full Random Data pattern, 4KB Align I/Os and test time duration was 15 minutes.

#### 3.2.2 SLC-Lite

Table 3-3: SLC-Lite Performance

| Capacity Performance   | 8 GB | 16 GB | 32 GB | 64 GB |

|------------------------|------|-------|-------|-------|

| Sustained read (MB/s)  | 150  | 130   | 300   | 500   |

| Sustained write (MB/s) | 95   | 80    | 160   | 185   |

<sup>\*\*</sup>Cylinders, heads or sectors are not applicable for these capacities. Only LBA addressing applies.

# 3.3 Environmental Specifications

Table 3-4 Environmental Specifications

| ltem                             | Specification  |

|----------------------------------|----------------|

| Operating temperature (Standard) | 0°C ~ 70°C     |

| Operating temperature (Extended) | -40°C ~ 85°C   |

| Storage temperature              | -40°C ~ 85°C   |

| ESD (Electrostatic Discharge)*   | 23°C, 49% (RH) |

| Acoustic                         | 0dB            |

<sup>\*</sup>Device functions are affected, but EUT will be back to its normal or operational state automatically.

## 3.4 Certification and Compliance

- CE

- FCC

- RoHS

- BSMI

# 4. Flash Management

#### 4.1 Error Correction/Detection

The ECC engine in this device can detect and correct up to 72 bits error in 1K bytes.

### 4.2 Flash Block Management

Bad blocks are blocks that include one or more invalid bits, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Initial Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named "Later Bad Blocks". Thus, this device implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages any bad blocks that appear with use. This practice further prevents data being stored into bad blocks and improves the data reliability.

### 4.3 Wear Leveling

NAND Flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some area get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Wear Leveling technique is applied to extend the lifespan of NAND Flash by evenly distributing write and erase cycles across the media. Apacer provides advanced Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static Wear Leveling algorithms, the life expectancy of the NAND Flash is greatly improved.

## 4.4 Power Failure Management

Power Loss Protection is a mechanism to prevent data loss during unexpected power failure. DRAM is a volatile memory and frequently used as temporary cache or buffer between the controller and the NAND flash to improve the SSD performance. However, one major concern of the DRAM is that it is not able to keep data during power failure. Accordingly, the  $\mu$ SDC applies the flushing mechanism which requests the controller to transfer data to the cache. For this  $\mu$ SDC, SDR performs as a cache, and its sizes include 8MB or 32MB. Only when the data is fully committed to the NAND flash will the controller send acknowledgement to the host. Such implementation can prevent false-positive performance and the risk of power cycling issues.

Additionally, it is critical for a controller to shorten the time the in-flight data stays in the cache. Thus, the  $\mu SDC$  applies an algorithm to reduce the amount of data resides in the cache to provide a better performance by allowing incoming data to only have a "pit stop" in the cache and then move to the NAND flash at once. If the flash is jammed due to particular file sizes (random 4K), the cache will be treated as an "organizer", consolidating incoming data into groups before written into the flash to improve write amplification.

In sum, with this power failure management, µSDC proves to provide the reliability required by consumer, industrial, and enterprise-level application.

#### 4.5 ATA Secure Erase

ATA Secure Erase is an ATA disk purging command currently embedded in most of the storage drives. Defined in ATA specifications, (ATA) Secure Erase is part of Security Feature Set that allows storage drives to erase all user data areas. The erase process usually runs on the firmware level as most of the ATA-based storage media currently in the market are built-in with this command. ATA Secure Erase can securely wipe out the user data in the drive and protects it from malicious attack.

#### 4.6 S.M.A.R.T.

SMART, an acronym for Self-Monitoring, Analysis and Reporting Technology, is an open standard that allows a hard disk drive to automatically detect its health and report potential failures. When a failure is recorded by SMART, users can choose to replace the drive to prevent unexpected outage or data loss. Moreover, SMART can inform users of impending failures while there is still time to perform proactive actions, such as copy data to another device.

#### **4.7 TRIM**

TRIM is a feature which helps improve the read/write performance and speed of solid-state drives (SSD). Unlike hard disk drives (HDD), SSDs are not able to overwrite existing data, so the available space gradually becomes smaller with each use. With the TRIM command, the operating system can inform the SSD which blocks of data are no longer in use and can be removed permanently. Thus, the SSD will perform the erase action, which prevents unused data from occupying blocks all the time.

## 4.8 SATA Power Management

By complying with SATA 6.0 Gb/s specifications, the SSD supports the following SATA power saving modes:

- ACTIVE: PHY ready, full power, Tx & Rx operational

- PARTIAL: Reduces power, resumes in under 10 μs (microseconds)

- SLUMBER: Reduces power, resumes in under 10 ms (milliseconds)

- DEVSLP (Device Sleep): triggered by interface signal, PHY might be powered down, the device in a almost shut down state, consuming less power than Slumber mode, host support required for this mode

Note: the behaviors of power management features would depend on host/device settings.

# 5. Software Interface

# 5.1 Command Set

| Code    | Command                           | Code | Command                   |

|---------|-----------------------------------|------|---------------------------|

| 00h     | NOP                               | 97h  | Idle                      |

| 06h     | Data Set Management               | 98h  | Check Power Mode          |

| 10h-1Fh | Recalibrate                       | 99h  | Sleep                     |

| 20h     | Read Sectors                      | B0h  | SMART                     |

| 21      | Read Sectors without Retry        | B1h  | Device Configurations     |

| 24h     | Read Sectors EXT                  | C4h  | Read Multiple             |

| 25h     | Read DMA EXT                      | C5h  | Write Multiple            |

| 27h     | Read Native Max Address EXT       | C6h  | Set Multiple Mode         |

| 29h     | Read Multiple EXT                 | C8h  | Read DMA                  |

| 2Fh     | Read Log EXT                      | C9h  | Read DMA without Retry    |

| 30h     | Write Sectors                     | CAh  | Write DMA                 |

| 31h     | Write Sectors without Retry       | CBh  | Write DMA without Retry   |

| 34h     | Write Sectors EXT                 | CEh  | Write Multiple FUA EXT    |

| 35h     | Write DMA EXT                     | E0h  | Standby Immediate         |

| 37h     | Set Native Max Address EXT        | E1h  | Idle Immediate            |

| 38h     | CFA Write Sectors without Erase   | E2h  | Standby                   |

| 39h     | Write Multiple EXT                | E3h  | Idle                      |

| 3Dh     | Write DMA FUA EXT                 | E4h  | Read Buffer               |

| 3Fh     | Write Long EXT                    | E5h  | Check Power Mode          |

| 40h     | Read Verify Sectors               | E6h  | Sleep                     |

| 41h     | Read Verify Sectors without Retry | E7h  | Flush Cache               |

| 42h     | Read Verify Sectors EXT           | E8h  | Write Buffer              |

| 45h     | Write Uncorrectable EXT           | EAh  | Flush Cache EXT           |

| 60h     | Read FPDMA Queued                 | ECh  | Identify Device           |

| 61h     | Write FPDMA Queued                | EFh  | Set Features              |

| 70h-7Fh | Seek                              | F1h  | Security Set Password     |

| 90h     | Execute Device Diagnostic         | F2h  | Security Unlock           |

| 91h     | Initialize Device Parameters      | F3h  | Security Erase Prepare    |

| 92h     | Download Microcode                | F4h  | Security Erase Unit       |

| 93h     | Download Microcode DMA            | F5h  | Security Freeze Lock      |

| 94h     | Standby Immediate                 | F6h  | Security Disable Password |

| 95h     | Idle Immediate                    | F8h  | Read Native Max Address   |

| 96h     | Standby                           | F9h  | Set Max Address           |

# 6. Electrical Specification

## **6.1 Operating Voltage**

Table 6-1 lists the supply voltage for  $\mu$ SDC.

Table 6-1: Operating Voltage

| Parameter | Voltage | Range           |

|-----------|---------|-----------------|

| VCC       | 3.3V    | 3.135V ~ 3.465V |

| VCCQ      | 1.8V    | 1.71V ~ 1.89V   |

| VDDC      | 1.2V    | 1.14V ~ 1.26V   |

| VDD       | 1.2V    | 1.14V ~ 1.26V   |

## **6.2 Power Consumption**

Table 6-2 lists the power consumption for  $\mu$ SDC.

#### 6.2.1 MLC

Table 6-2: Power Consumption Based on 3.3V (typical)

| Capacity    | 8 GB | 16 GB | 32 GB | 64 GB | 128 GB |

|-------------|------|-------|-------|-------|--------|

| Active (mA) | 170  | 200   | 255   | 250   | 445    |

| Idle (mA)   | 70   | 70    | 70    | 75    | 75     |

Note: Results may differ from various flash configurations or platforms.

#### 6.2.1 SLC-Lite

Table 6-3: Power Consumption Based on 3.3V (typical)

| Capacity    | 8 GB | 16 GB | 32 GB | 64 GB |

|-------------|------|-------|-------|-------|

| Active (mA) | 260  | 270   | 330   | 325   |

| Idle (mA)   | 75   | 45    | 105   | 80    |

Note: Results may differ from various flash configurations or platforms.

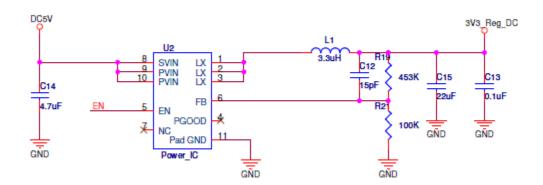

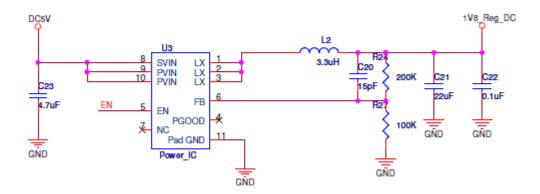

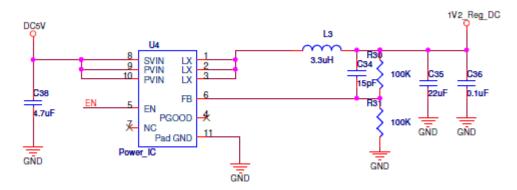

## 6.1 µSDC Power Current & Circuit

Since the  $\mu SDC$  operates on 3 levels of voltage requirements: 3.3V, 1.8V and 1.2V, the power current measurements were conducted respectively.

**Typical Power Consumption**

| 8GB      | 3.3v   | 1.8v   | 1.2v   | 16GB     | 3.3v   | 1.8v   | 1.2v   |

|----------|--------|--------|--------|----------|--------|--------|--------|

| Power-on | 100 mA | 80 mA  | 300 mA | Power-on | 100 mA | 80 mA  | 300 mA |

| Idle     | 35 mA  | 100 uA | 150 mA | ldle     | 35 mA  | 100 uA | 150 mA |

| Active   | 100 mA | 80 mA  | 350 mA | Active   | 140 mA | 100 mA | 380 mA |

| 32GB     | 3.3v   | 1.8v   | 1.2v   | 64GB     | 3.3v   | 1.8v   | 1.2v   |

| Power-on | 100 mA | 80 mA  | 300 mA | Power-on | 100 mA | 150 mA | 300 mA |

| Idle     | 35 mA  | 150 uA | 150 mA | ldle     | 35 mA  | 400 uA | 150 mA |

| Active   | 220 mA | 130 mA | 460 mA | Active   | 220 mA | 170 mA | 460 mA |

Notes: The results of "typical" power consumption were based on the maximum value measured from the experiment.

#### +3V3 Circuit

#### +1V8 Circuit

#### +1V2 Circuit

Notes: the Power IC used in the diagrams above is able to deliver up to 3A output current in case of changes or replacement in NAND Flash memories.

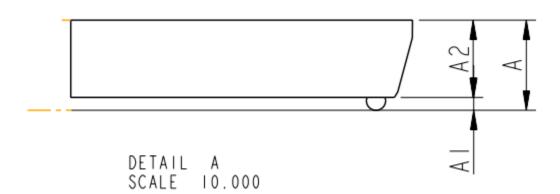

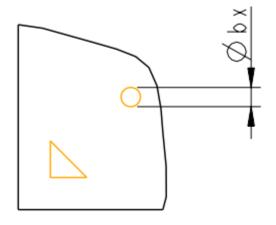

# 7. Mechanical Specifications

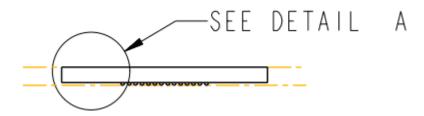

DETAIL B SCALE 10.000

|        | Dimension |      |       |

|--------|-----------|------|-------|

| Symbol | MIN       | NOM  | MAX   |

| Α      |           |      | 1.40  |

| ΑΙ     | 0.15      |      |       |

| A 2    |           |      | 1.20  |

| D      | 15.85     | 16   | 16.15 |

| E      | 19.85     | 20   | 20.15 |

| DΙ     |           | 1.5  |       |

| D2     |           | 3.5  |       |

| D3     |           | 5.5  |       |

| D 4    |           | 6.5  |       |

| D 5    |           | 8.5  |       |

| D6     |           | 10.5 |       |

| D 7    |           | 12.5 |       |

| ΕI     |           | 6.5  |       |

| E 2    |           | 10.5 |       |

| E 3    |           | 12.5 |       |

| E 4    |           | 13.5 |       |

| E 5    |           | 14.5 |       |

| E 6    |           | 16.5 |       |

| е      |           | 0.50 |       |

| b      | 0.25      | 0.30 | 0.35  |

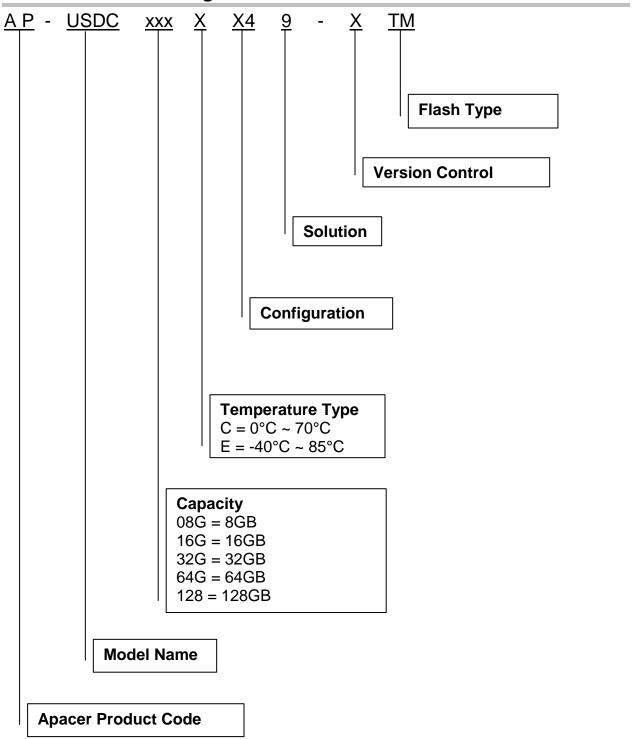

# **8. Product Ordering Information**

## 8.1 Product Code Designation

## **8.2 Valid Combination**

#### A. MLC

## 8.2.1 Standard Temperature (0°C ~ 70°C)

| Capacity | Part Number        | Top Side Marking |

|----------|--------------------|------------------|

| 8GB      | AP-USDC08GC149-KTM | SH9B-8GDCA110B   |

| 16GB     | AP-USDC16GC249-KTM | SH9B-16GDCA220B  |

| 32GB     | AP-USDC32GC449-KTM | SH9B-32GDCA440B  |

| 64GB     | AP-USDC64GC449-KTM | SH9B-64GDCB440B  |

| 128GB    | AP-USDC128C849-KTM | SH9B-128DCB480B  |

## 8.2.2 Extended Temperature (-40°C ~ 85°C)

| Capacity | Part Number        | Top Side Marking |

|----------|--------------------|------------------|

| 8GB      | AP-USDC08GE149-KTM | SH9B-8GDEA110B   |

| 16GB     | AP-USDC16GE249-KTM | SH9B-16GDEA220B  |

| 32GB     | AP-USDC32GE449-KTM | SH9B-32GDEA440B  |

| 64GB     | AP-USDC64GE449-KTM | SH9B-64GDEB440B  |

| 128GB    | AP-USDC128E849-KTM | SH9B-128DEB480B  |

#### **B. SLC-Lite**

## 8.2.3 Standard Temperature (0°C ~ 70°C)

| Capacity | Part Number        | Top Side Marking |

|----------|--------------------|------------------|

| 8GB      | AP-USDC08GC249-LTM | SH9B-8GDCA22LB   |

| 16GB     | AP-USDC16GC449-LTM | SH9B-16GDCA44LB  |

| 32GB     | AP-USDC32GC449-LTM | SH9B-32GDCB44LB  |

| 64GB     | AP-USDC064C849-LTM | SH9B-64GDCB48LB  |

#### 8.2.4 Extended Temperature (-40°C ~ 85°C)

| Capacity | Part Number        | Top Side Marking |

|----------|--------------------|------------------|

| 8GB      | AP-USDC08GE249-LTM | SH9B-8GDEA22LB   |

| 16GB     | AP-USDC16GE449-LTM | SH9B-16GDEA44LB  |

| 32GB     | AP-USDC32GE449-LTM | SH9B-32GDEB44LB  |

| 64GB     | AP-USDC064E849-LTM | SH9B-64GDEB48LB  |

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your Apacer sales representative to confirm availability of valid combinations and to determine availability of new combinations.

# **Revision History**

| Revision | Date      | Description      | Remark |

|----------|-----------|------------------|--------|

| 1.0      | 11/6/2015 | Official release |        |

# **Global Presence**

Taiwan (Headquarters) Apacer Technology Inc.

1F., No.32, Zhongcheng Rd., Tucheng Dist.,

New Taipei City 236, Taiwan R.O.C.

Tel: 886-2-2267-8000 Fax: 886-2-2267-2261 amtsales@apacer.com

U.S.A. Apacer Memory America, Inc.

46732 Lakeview Blvd., Fremont, CA 94538

Tel: 1-408-518-8699 Fax: 1-510-249-9568 <u>sa@apacerus.com</u>

Japan Apacer Technology Corp.

5F, Matsura Bldg., Shiba, Minato-Ku

Tokyo, 105-0014, Japan Tel: 81-3-5419-2668 Fax: 81-3-5419-0018 jpservices@apacer.com

Europe Apacer Technology B.V.

Science Park Eindhoven 5051 5692 EB Son,

The Netherlands Tel: 31-40-267-0000 Fax: 31-40-267-0000#6199

sales@apacer.nl

China Apacer Electronic (Shanghai) Co., Ltd

Room D, 22/FL, No.2, Lane 600, JieyunPlaza, Tianshan RD, Shanghai, 200051, China

Tel: 86-21-6228-9939

Fax: 86-21-6228-9936 sales@apacer.com.cn

India Apacer Technologies Pvt Ltd,

Unit No.201, "Brigade Corner", 7<sup>th</sup> Block Jayanagar,

Yediyur Circle, Bangalore - 560082, India

Tel: 91-80-4152-9061 Fax: 91-80-4170-0215 sales india@apacer.com