## **RoHS Compliant**

# **Anti-Sulfuration PCI Express Flash Drive**

Industrial PV220-M280 BiCS5 Product Specifications

January 11, 2024

Version 1.4

**Apacer Technology Inc.**

1F, No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City, Taiwan, R.O.C Tel: +886-2-2267-8000 Fax: +886-2-2267-2261 www.apacer.com

## **Specifications Overview:**

#### PCle Interface

- Compliant with PCI Express 3.1

- Compliant with NVMe 1.3

- Compatible with PCIe Gen3 x4 interface

#### Capacity

- Single-sided: 120, 240 GB

- Double-sided: 480, 960, 1920 GB

#### Performance<sup>1</sup>

- Interface burst read/write: 4 GB/sec

- Sequential read: up to 2,400 MB/sec

- Sequential write: up to 2,230 MB/sec

- Random read (4K): up to 212,000 IOPS

- Random write (4K): up to 331,000 IOPS

#### • Flash Management

- Low-Density Parity-Check (LDPC) Code

- Global Wear Leveling

- Flash bad-block management

- Flash Translation Layer: Page Mapping

- S.M.A.R.T.

- DataDefender<sup>™</sup>

- TRIM

- Hyper Cache Technology

- Over-provisioning

- DataRAID™

- NVMe Secure Erase

#### NVMe Features<sup>2</sup>

- Supports HMB (Host Memory Buffer)

- NAND Flash Type: 3D TLC (BiCS5)

- MTBF: >3,000,000 hours

### • Endurance (in drive writes per day: DWPD)

- 120 GB: 2.1 DWPD

- 240 GB: 2.13 DWPD

- 480 GB: 2.25 DWPD

- 960 GB: 1.95 DWPD

- 1920 GB: 1.83 DWPD

#### Temperature Range

- Operating:

- Standard: 0°C to 70°C

- Wide: -40°C to 85°C

- Storage: -55°C to 100°C

### Supply Voltage

$-3.3V \pm 5\%$

#### Power Consumption<sup>1</sup>

- Active mode (Max.): 1,235 mA

- Idle mode: 235 mA

#### Connector Type

- 75-pin M.2 module pinout

### Power Management

- Supports APST

- Supports ASPM L1.2

#### Security

AES 256-bit hardware encryption

### Reliability

- Thermal Sensor

- Thermal Throttling

- End-to-End Data Protection

- CoreGlacier<sup>TM</sup>

- Anti-Sulfuration

- Sidefill

### Physical Characteristics

- Form factor:

- Single-sided M.2 2280-M

- Double-sided M.2 2280-M

- Dimensions (unit: mm):

- Single-sided: 22.00 x 80.00 x 2.58(max.)

- Double-sided: 22.00 x 80.00 x 4.08(max.)

- Net weight:  $7.7g \pm 5\%$

#### LED Indicators for Drive Behavior

### RoHS Compliant

#### Notes:

- Varies from capacities. The values for performances and power consumptions presented are typical and may vary depending on flash configurations or platform settings.

- Windows 10 (version 1703) onwards supports the HMB (Host Memory Buffer) function.

## **Table of Contents**

| 1. General Description                     | 4  |

|--------------------------------------------|----|

| 2. Functional Block                        | 5  |

| 3. Pin Assignments                         | 6  |

| 4. Product Specifications                  |    |

| -                                          |    |

| 4.1 Capacity                               |    |

| 4.3 Environmental Specifications           |    |

| 4.4 Mean Time Between Failures (MTBF)      |    |

| 4.5 Certification and Compliance           |    |

| 4.6 Endurance                              |    |

| 4.7 LED Indicator Behavior.                |    |

|                                            |    |

| 5. Flash Management                        | 12 |

| 5.1 Error Correction/Detection             | 12 |

| 5.2 Bad Block Management                   | 12 |

| 5.3 Global Wear Leveling                   | 12 |

| 5.4 DataDefender™                          | 12 |

| 5.5 TRIM                                   | 12 |

| 5.6 Flash Translation Layer – Page Mapping | 13 |

| 5.7 Hyper Cache Technology                 | 13 |

| 5.8 Over-provisioning                      | 13 |

| 5.9 DataRAID™                              | 13 |

| 5.10 NVMe Secure Erase                     | 13 |

| 6. NVMe Support Features                   | 14 |

| 6.1 Host Memory Buffer                     |    |

| 7. Security and Reliability Features       | 15 |

| 7.1 Anti-Sulfuration                       | 15 |

| 7.2 Advanced Encryption Standard           | 15 |

| 7.3 Thermal Sensor                         | 15 |

| 7.4 Thermal Throttling                     | 15 |

| 7.5 End-to-End Data Protection             | 16 |

| 7.6 CaraClasiarTM                          | 16 |

# Apacer

| 7.7 Sidefill                     | 16 |

|----------------------------------|----|

| 8. Software Interface            | 17 |

| 8.1 Command Set                  | 17 |

| 8.2 S.M.A.R.T.                   | 18 |

| 9. Electrical Specifications     | 20 |

| 9.1 Operating Voltage            | 20 |

| 9.2 Power Consumption            | 20 |

| 10. Mechanical Specifications    | 21 |

| 10.1 Single-sided Dimensions     | 21 |

| 10.2 Double-sided Dimensions     | 22 |

| 11. Product Ordering Information | 23 |

| 11.1 Product Code Designations   | 23 |

| 11.2 Valid Combinations          | 24 |

## 1. General Description

Apacer PV220-M280 is the fastest SSD designed as M.2 2280 mechanical dimensions which provides full compliance with PCIe Gen3 x4 interface and NVMe 1.3 specifications, allowing it to operate in power management modes and greatly save on power consumption. Built with a powerful PCIe controller that supports on-the-module ECC as well as efficient wear leveling scheme, PV220-M280 delivers outstanding performance in data transfer. With the compact and high-speed storage, PV220-M280 is the ideal choice for larger, faster hosts deployed in a wide range of applications that require outstanding performance.

Featuring anti-sulfuration technology, PV220-M280 not only uses special alloy materials but also achieves a complete air barrier through rigorously inspected special materials and technologies in compliance with the ANSI/ISA 71.04-2013 standard to increase system lifetime and ensure product reliability and durability.

Utilizing 3D NAND for higher capacity up to 1920GB and providing more power efficiency than 2D NAND, PV220-M280 is not only implemented with LDPC (Low Density Parity Check) ECC engine to extend SSD endurance and increase data reliability, but also equipped with a built-in thermal sensor to monitor the temperature of the SSD via S.M.A.R.T commands and configured with thermal throttling to dynamically adjust frequency scaling to enhance data reliability and provide sustained performance while overheating. To ensure that products continue to operate normally in high vibration and under extreme environmental changes, Apacer provides Sidefill technology to increase product reliability and resistance to thermal and mechanical stress. CoreGlacier is also available to keep the temperature low, while still allowing the drive to deliver high-speed performance. For highly-intensive applications, End-to-End Data Protection ensures that data integrity can be assured at multiple points in the path to enable reliable delivery of data transfers.

In terms of security, Advanced Encryption Standard (AES) ensures data security and provides users with peace of mind knowing their data is safeguarded at all times. PV220-M280 also adopts the latest page mapping file translation layer and comes with various implementations including power saving modes, wear leveling, flash block management, S.M.A.R.T., TRIM, Hyper Cache tech flash block management, DataDefender, TRIM, power saving modes, Hyper Cache technology, over-provisioning, DataRAID, and NVMe secure erase.

With its exceptional performance, trustable reliability, and enhanced data protection, PV220-M280 is definitely the ideal storage or cache solution for a variety of applications ranging from industrial, imaging, computing to enterprise markets.

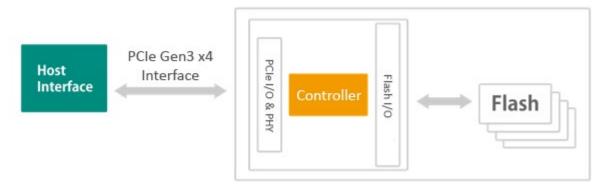

## 2. Functional Block

Note: The actual number of NAND flash used on Apacer PV220-M280 varies from capacities. The illustration is for reference only.

Figure 2-1 Functional Block Diagram

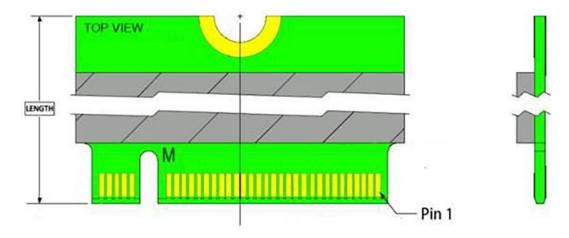

## 3. Pin Assignments

This connector does not support hot plug capability. There are a total of 75 pins. 12 pin locations are used for mechanical key locations; this allows such a module to plug into Key M connectors.

**Figure 3-1 Pin Connectors**

**Table 3-1 Pin Assignments**

|         |                        | no o i i in 7.001gililionto                                                                                                                                      |

|---------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Туре                   | Description                                                                                                                                                      |

| 1       | GND                    | Ground                                                                                                                                                           |

| 2       | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 3       | GND                    | Ground                                                                                                                                                           |

| 4       | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 5       | PETn3                  | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                                                  |

| 6       | PWRDIS (I)(0/1.8/3.3V) | No connect                                                                                                                                                       |

| 7       | PETp3                  | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                                                  |

| 8       | PLN# (I)(0/1.8/3.3V)   | Reserved for Apacer use only <sup>1</sup>                                                                                                                        |

| 9       | GND                    | Ground                                                                                                                                                           |

| 10      | LED1#                  | Open drain, active low signal. These signals are used to allow the add-in card to provide status indicators via LED devices that will be provided by the system. |

| 11      | PERn3                  | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                                                  |

| 12      | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 13      | PERp3                  | PCIe RX Differential signals defined by the PCI Express M.2 spec                                                                                                 |

| 14      | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 15      | GND                    | Ground                                                                                                                                                           |

| 16      | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 17      | PETn2                  | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                                                  |

| 18      | 3.3 V                  | 3.3V source                                                                                                                                                      |

| 19      | PETp2                  | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                                                  |

| 20      | NC                     | No connect                                                                                                                                                       |

**Table 3-1 Pin Assignments**

| Pin No. | Туре                       | Description                                                                                                                    |

|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 21      | GND                        | Ground                                                                                                                         |

| 22      | VIO 1.8 V                  | No connect                                                                                                                     |

| 23      | PERn2                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 24      | NC                         | No connect                                                                                                                     |

| 25      | PERp2                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 26      | NC                         | No connect                                                                                                                     |

| 27      | GND                        | Ground                                                                                                                         |

| 28      | NC                         | Reserved for Apacer use only <sup>1</sup>                                                                                      |

| 29      | PETn1                      | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                |

| 30      | PLA_S3# (O)(0/1.8/3.3V)    | Reserved for Apacer use only <sup>1</sup>                                                                                      |

| 31      | PETp1                      | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                |

| 32      | GND                        | No connect                                                                                                                     |

| 33      | GND                        | Ground                                                                                                                         |

| 34      | USB_D+                     | No connect                                                                                                                     |

| 35      | PERn1                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 36      | USB_D-                     | No connect                                                                                                                     |

| 37      | PERp1                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 38      | GND                        | No connect                                                                                                                     |

| 39      | GND                        | Ground                                                                                                                         |

| 40      | SMB_CLK (I/O)(0/1.8V)      | No connect                                                                                                                     |

| 41      | PETn0                      | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                |

| 42      | SMB_DATA (I/O)(0/1.8V)     | No connect                                                                                                                     |

| 43      | PETp0                      | PCIe TX Differential signal defined by the PCI Express M.2 spec                                                                |

| 44      | ALERT# (O)(0/1.8V)         | No connect                                                                                                                     |

| 45      | GND                        | Ground                                                                                                                         |

| 46      | NC                         | No connect                                                                                                                     |

| 47      | PERn0                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 48      | NC                         | No connect                                                                                                                     |

| 49      | PERp0                      | PCIe RX Differential signal defined by the PCI Express M.2 spec                                                                |

| 50      | PERST# (I)(0/1.8V/3.3V)    | PE-Reset is a functional reset to the card as specification.  defined by the PCIe Mini CEM                                     |

| 51      | GND                        | Ground                                                                                                                         |

| 52      | CLKREQ# (I/O)(0/1.8V/3.3V) | Clock Request is a reference clock request signal as defined by the PCle Mini CEM specification; Also used by L1 PM Substates. |

| 53      | REFCLKn                    | PCIe Reference Clock signals (100 MHz) spec. defined by the PCI Express M.2                                                    |

| 54      | PEWAKE# (I/O)(0/1.8V/3.3V) | No connect                                                                                                                     |

| 55      | REFCLKp                    | PCIe Reference Clock signals (100 MHz) spec. defined by the PCI Express M.2                                                    |

| 56      | Reserved for MFG_DATA      | Reserved for Apacer use only <sup>1</sup>                                                                                      |

| 57      | GND                        | Ground                                                                                                                         |

| 58      | Reserved for MFG_CLOCK     | Reserved for Apacer use only <sup>1</sup>                                                                                      |

| 59      | Module Key M               | Module Key                                                                                                                     |

# Apacer

**Table 3-1 Pin Assignments**

| Pin No. | Туре                    | Description                               |

|---------|-------------------------|-------------------------------------------|

| 60      | Module Key M            | Module Key                                |

| 61      | Module Key M            | Module Key                                |

| 62      | Module Key M            | Module Key                                |

| 63      | Module Key M            | Module Key                                |

| 64      | Module Key M            | Module Key                                |

| 65      | Module Key M            | Module Key                                |

| 66      | Module Key M            | Module Key                                |

| 67      | NC                      | Reserved for Apacer use only <sup>1</sup> |

| 68      | SUSCLK (I)(0/1.8V/3.3V) | No connect                                |

| 69      | PEDET                   | No connect                                |

| 70      | 3.3 V                   | 3.3V source                               |

| 71      | GND                     | Ground                                    |

| 72      | 3.3 V                   | 3.3V source                               |

| 73      | VIO_CFG (O)             | Ground                                    |

| 74      | 3.3 V                   | 3.3V source                               |

| 75      | GND                     | Ground                                    |

Note: 1. Reserved by Apacer, please do not connect to a host.

## 4. Product Specifications

## 4.1 Capacity

Capacity specifications of PV220-M280 are available as shown in Table 4-1.

**Table 4-1 Capacity Specifications**

| Capacity | Total bytes       | Total LBA     |

|----------|-------------------|---------------|

| 120 GB   | 120,034,123,776   | 234,441,648   |

| 240 GB   | 240,057,409,536   | 468,862,128   |

| 480 GB   | 480,103,981,056   | 937,703,088   |

| 960 GB   | 960,197,124,096   | 1,875,385,008 |

| 1920 GB  | 1,920,383,410,176 | 3,750,748,848 |

#### Notes:

- Display of total bytes varies from operating systems.

- 1 GB = 1,000,000,000 bytes; 1 sector = 512 bytes.

- LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the

lifespan of the device. However, the total usable capacity of the SSD is most likely to be less than the total physical

capacity because a small portion of the capacity is reserved for device maintenance usages.

### 4.2 Performance

Performance of PV220-M280 is listed below in Table 4-2.

**Table 4-2 Performance Specifications**

| Capacity Performance    | 120 GB  | 240 GB  | 480 GB  | 960 GB  | 1920 GB |

|-------------------------|---------|---------|---------|---------|---------|

| Sequential Read (MB/s)  | 1,060   | 2,185   | 2,400   | 2,190   | 2,065   |

| Sequential Write (MB/s) | 545     | 1,125   | 2,105   | 2,230   | 2,020   |

| 4K Random Read (IOPS)   | 48,000  | 90,000  | 178,000 | 212,000 | 200,000 |

| 4K Random Write (IOPS)  | 103,000 | 182,000 | 293,000 | 331,000 | 271,000 |

### Notes:

- Results may differ from various flash configurations or host system setting.

- Sequential read/write is based on CrystalDiskMark 8.0.4 with file size 1,000MB.

- Random read/write is measured using IOMeter with Queue Depth 128.

## **4.3 Environmental Specifications**

Environmental specifications of PV220-M280 are shown in Table 4-3.

**Table 4-3 Environmental Specifications**

| Parameter   | Туре          | Specifications                                                        |

|-------------|---------------|-----------------------------------------------------------------------|

| Tomporatura | Operating     | 0°C to 70°C (Standard); -40°C to 85°C (Wide)                          |

| Temperature | Non-operating | -55°C to 100°C                                                        |

| Vibration   | Operating     | 7.69 GRMS, 20~2000 Hz/random (compliant with MIL-STD-810G)            |

| VIDIALION   | Non-operating | 4.02 GRMS, 15~2000 Hz/random (compliant with MIL-STD-810G)            |

| Shock       | Operating     | Acceleration, 50(G)/11(ms)/half sine (compliant with MIL-STD-202G)    |

| SHOCK       | Non-operating | Acceleration, 1500(G)/0.5(ms)/half sine (compliant with MIL-STD-883K) |

Note: This Environmental Specification table indicates the conditions for testing the device. Real world usages may affect the results.

## 4.4 Mean Time Between Failures (MTBF)

Mean Time Between Failures (MTBF) is predicted based on reliability data for the individual components in PV220-M280. The prediction result for PV220-M280 is more than 3,000,000 hours.

Note: The MTBF is predicated and calculated based on "Telcordia Technologies Special Report, SR-332, Issue 3" method.

## 4.5 Certification and Compliance

PV220-M280 complies with the following standards:

- CE

- UKCA

- FCC

- RoHS

- MIL-STD-810G

### 4.6 Endurance

The endurance of a storage device is predicted by Drive Writes Per Day based on several factors related to usage, such as the amount of data written into the drive, block management conditions, and daily workload for the drive. Thus, key factors, such as Write Amplifications and the number of P/E cycles, can influence the lifespan of the drive.

**Table 4-4 Endurance Specifications**

| Capacity | Drive Writes Per Day |

|----------|----------------------|

| 120 GB   | 2.1                  |

| 240 GB   | 2.13                 |

| 480 GB   | 2.25                 |

| 960 GB   | 1.95                 |

| 1920 GB  | 1.83                 |

#### Notes:

- This estimation complies with JEDEC JESD-219, enterprise endurance workload of random data with payload size distribution.

- Flash vendor guaranteed 3D NAND TLC P/E cycle: 3K

- WAF may vary from capacity, flash configurations and writing behavior on each platform.

- 1 Terabyte = 1,024GB

- DWPD (Drive Writes Per Day) is calculated based on the number of times that user overwrites the entire capacity of an SSD per day of its lifetime during the warranty period. (3D NAND TLC warranty: 3 years)

### 4.7 LED Indicator Behavior

The behavior of the PV220-M280 LED indicators is described in Table 4-5.

**Table 4-5 LED Behavior**

| Location | LED | Description                                 |

|----------|-----|---------------------------------------------|

| LED A    | DAS | LED blinks when the drive is being accessed |

## 5. Flash Management

### 5.1 Error Correction/Detection

PV220-M280 implements a hardware ECC scheme, based on the Low Density Parity Check (LDPC). LDPC is a class of linear block error correcting code which has apparent coding gain over BCH code because LDPC code includes both hard decoding and soft decoding algorithms. With the error rate decreasing, LDPC can extend SSD endurance and increase data reliability while reading raw data inside a flash chip.

## 5.2 Bad Block Management

Current production technology is unable to guarantee total reliability of NAND flash memory array. When a flash memory device leaves factory, it comes with a minimal number of initial bad blocks during production or out-of-factory as there is no currently known technology that produce flash chips free of bad blocks. In addition, bad blocks may develop during program/erase cycles. Since bad blocks are inevitable, the solution is to keep them in control. Apacer flash devices are programmed with ECC, page mapping technique and S.M.A.R.T to reduce invalidity or error. Once bad blocks are detected, data in those blocks will be transferred to free blocks and error will be corrected by designated algorithms.

## 5.3 Global Wear Leveling

Flash memory devices differ from Hard Disk Drives (HDDs) in terms of how blocks are utilized. For HDDs, when a change is made to stored data, like erase or update, the controller mechanism on HDDs will perform overwrites on blocks. Unlike HDDs, flash blocks cannot be overwritten and each P/E cycle wears down the lifespan of blocks gradually. Repeatedly program/erase cycles performed on the same memory cells will eventually cause some blocks to age faster than others. This would bring flash storages to their end of service term sooner. Global wear leveling is an important mechanism that levels out the wearing of all blocks so that the wearing-down of all blocks can be almost evenly distributed. This will increase the lifespan of SSDs.

### 5.4 DataDefender™

Apacer's DataDefender is an advanced technology of power failure management which combines both firmware and hardware mechanisms to ensure data integrity. When power disruption occurs, the low voltage detector will be triggered. When this happens, the SSD's protection mechanism is activated and cuts off data transmission from the host. Once the power supply is resumed, the firmware protection mechanism will ensure the integrity of the firmware as well as the data already written into the NAND flash media.

#### **5.5 TRIM**

TRIM is a feature which helps improve the read/write performance and speed of solid-state drives (SSD). Unlike hard disk drives (HDD), SSDs are not able to overwrite existing data, so the available space gradually becomes smaller with each use. With the TRIM command, the operating system can inform the SSD which blocks of data are no longer in use and can be removed permanently. Thus, the SSD will perform the erase action, which prevents unused data from occupying blocks all the time.

## 5.6 Flash Translation Layer – Page Mapping

Page mapping is an advanced flash management technology whose essence lies in the ability to gather data, distribute the data into flash pages automatically, and then schedule the data to be evenly written. Page-level mapping uses one page as the unit of mapping. The most important characteristic is that each logical page can be mapped to any physical page on the flash memory device. This mapping algorithm allows different sizes of data to be written to a block as if the data is written to a data pool and it does not need to take extra operations to process a write command. Thus, page mapping is adopted to increase random access speed and improve SSD lifespan, reduce block erase frequency, and achieve optimized performance and lifespan.

## **5.7 Hyper Cache Technology**

Apacer proprietary Hyper Cache technology uses a portion of the available capacity as SLC (1bit-percell) NAND flash memory, called Hyper cache mode. When data is written to SSD, the firmware will direct the data to Hyper Cache mode, providing excellent performance to handle various scenarios in industrial use.

## 5.8 Over-provisioning

Over-provisioning (OP) is a certain portion of the SSD capacity exclusively for increasing Garbage Collection (GC) efficiency, especially when the SSD is filled to full capacity or performs a heavy mixed-random workload. OP has the advantages of providing extended life expectancy, reliable data integrity, and high sustained write performance.

## 5.9 DataRAID™

Apacer's DataRAID algorithm applies an additional level of protection and error-checking. Using this algorithm, a certain amount of space is given over to aggregating and resaving the existing parity data used for error checking. So, in the event that data becomes corrupted, the parity data can be compared to the existing uncorrupted data and the content of the corrupted data can be rebuilt.

### 5.10 NVMe Secure Erase

NVMe Secure Erase is an NVMe drive sanitize command currently embedded in most of the storage drives. Defined in NVMe specifications, NVMe Secure Erase is part of Format NVM command that allows storage drives to erase all user data areas. The erase process usually runs on the firmware level as most of the NVMe-based storage media currently in the market are built-in with this command. NVMe Secure Erase can securely wipe out the user data in the drive and protects it from malicious attack.

## **6. NVMe Support Features**

## **6.1 Host Memory Buffer**

Host Memory Buffer (HMB) allows HOST to allocate system memory for SSD's exclusive use in order to provide better performance and endurance, especially for DRAMless solutions.

## 7. Security and Reliability Features

### 7.1 Anti-Sulfuration

Apacer's awarded patent for anti-sulfuration products adopts exclusive and improved alloy materials to protect silver in the electrode from reacting with sulfur to produce silver sulfide and cause an increase in resistance. This technology not only effectively solves corrosion problems caused by environmental pollution but also increases overall system lifespan and allows stable system operation over long hours in a harsh environment, ensuring product reliability and durability.

Apacer's anti-sulfuration SSDs achieve a complete air barrier through strict inspection of special materials and technologies. After two complete accelerated verification tests of MFG (Mixed Fluid Gas) and FoS (Flower of Sulfur), it has passed the American National Standards Institute/International Association of Automation 71.04 G3 air corrosion certification. This proves that it has reached the industry's highest level of sulfur resistance, including resistance to silver corrosion, copper corrosion and creep.

## 7.2 Advanced Encryption Standard

Advanced Encryption Standard (AES) is a specification for the encryption of electronic data. AES has been adopted by the U.S. government since 2001 to protect classified information and is now widely implemented in embedded computing applications. The AES algorithm used in software and hardware is symmetric so that encrypting/decrypting requires the same encryption key. Without the key, the encrypted data is inaccessible to ensure information security.

Notably in flash memory applications, AES 256-bit hardware encryption is the mainstream to protect sensitive or confidential data. The hardware encryption provides better performance, reliability, and security than software encryption. It uses a dedicated processor, which is built inside the controller, to process the encryption and decryption. This enormously shortens the processing time and makes it efficient.

### 7.3 Thermal Sensor

Apacer Thermal Sensor is a digital temperature sensor with serial interface. By using designated pins for transmission, storage device owners are able to read temperature data.

## 7.4 Thermal Throttling

Thermal throttling can monitor the temperature of the SSD equipped with a built-in thermal sensor via S.M.A.R.T. commands. This method can ensure the temperature of the device stays within temperature limits by drive throttling, i.e. reducing the speed of the drive when the device temperature reaches the threshold level, so as to prevent overheating, guarantee data reliability, and prolong product lifespan. When the temperature exceeds the maximum threshold level, thermal throttling will be triggered to reduce performance step by step to prevent hardware components from being damaged. Performance is only permitted to drop to the extent necessary for recovering a stable temperature to cool down the device's temperature. Once the temperature decreases to the minimum threshold value, transfer speeds will rise back to its optimum performance level.

### 7.5 End-to-End Data Protection

End-to-End Data Protection is a feature implemented in Apacer SSD products that extends error control to cover the entire path from the host computer to the drive and back, and that ensures data integrity at multiple points in the path to enable reliable delivery of data transfers. Unlike ECC which does not exhibit the ability to determine the occurrence of errors throughout the process of data transmission, End-to-End Data Protection allows SSD controller to identify an error created anywhere in the path and report the error to the host computer before it is written to the drive. This error-checking and error-reporting mechanism therefore guarantees the trustworthiness and reliability of the SSD.

### 7.6 CoreGlacier™

In many applications, SSDs are subject to challenging conditions. If the working environment is already hot, and the SSD's operation causes it to increase in temperature as well, the result could be damage to the hardware or corrupted data. In cases like this, leading industrial manufacturers know to turn to Apacer. Apacer developed CoreGlacier, a heatsink that distributes dissipation in isolated components with no thermal diffusion, to prevent heat-related damage from occurring.

### 7.7 Sidefill

Apacer's sidefill technology strengthens the connections between solder joints and their board, making them more robust and vibration-resistant. It also allows for heat dissipation to offset thermal damage.

## 8. Software Interface

## 8.1 Command Set

Table 8-1 summarizes the commands supported by PV220-M280.

**Table 8-1 Admin Commands**

| Opcode | Command Description         |

|--------|-----------------------------|

| 00h    | Delete I/O Submission Queue |

| 01h    | Create I/O Submission Queue |

| 02h    | Get Log Page                |

| 04h    | Delete I/O Completion Queue |

| 05h    | Create I/O Completion Queue |

| 06h    | Identify                    |

| 08h    | Abort                       |

| 09h    | Set Features                |

| 0Ah    | Get Features                |

| 0Ch    | Asynchronous Event Request  |

| 10h    | Firmware Activate           |

| 11h    | Firmware Image Download     |

| 14h    | Device Self-test            |

Table 8-2 Admin Commands – NVM Command Set Specific

| Opcode | Command Description |

|--------|---------------------|

| 80h    | Format NVM          |

| 84h    | Sanitize            |

**Table 8-3 NVM Commands**

| Opcode | Command Description |

|--------|---------------------|

| 00h    | Flush               |

| 01h    | Write               |

| 02h    | Read                |

| 04h    | Write Uncorrectable |

| 05h    | Compare             |

| 09h    | Dataset Management  |

## 8.2 S.M.A.R.T.

SMART, an acronym for Self-Monitoring, Analysis and Reporting Technology, is an open standard that allows a hard disk drive to automatically detect its health and report potential failures. When a failure is recorded by SMART, users can choose to replace the drive to prevent unexpected outage or data loss. Moreover, SMART can inform users of impending failures while there is still time to perform proactive actions, such as copy data to another device.

Table 8-4 SMART (02h)

| Byte    | Length | Description                                             |  |  |

|---------|--------|---------------------------------------------------------|--|--|

| 0       | 1      | Critical Warning                                        |  |  |

| 1-2     | 2      | Composite Temperature (PCB Sensor)                      |  |  |

| 3       | 1      | Available Spare                                         |  |  |

| 4       | 1      | Available Spare Threshold                               |  |  |

| 5       | 1      | Percentage Used (Average Erase Count / P/E Cycle Count) |  |  |

| 6-31    | 26     | Reserved                                                |  |  |

| 32-47   | 16     | Data Units Read                                         |  |  |

| 48-63   | 16     | Data Units Written                                      |  |  |

| 64-79   | 16     | Host Read Commands                                      |  |  |

| 80-95   | 16     | Host Write Commands                                     |  |  |

| 96-111  | 16     | Controller Busy Time                                    |  |  |

| 112-127 | 16     | Power Cycles                                            |  |  |

| 128-143 | 16     | Power On Hours                                          |  |  |

| 144-159 | 16     | Unsafe Shutdowns                                        |  |  |

| 160-175 | 16     | Media and Data Integrity Errors                         |  |  |

| 176-191 | 16     | Number of Error Information Log Entries                 |  |  |

| 192-195 | 4      | Warning Composite Temperature Time                      |  |  |

| 196-199 | 4      | Critical Composite Temperature Time                     |  |  |

| 200-201 | 2      | Temperature Sensor 1: Controller Temperature            |  |  |

| 202-203 | 2      | Temperature Sensor 2: PCB Temperature                   |  |  |

| 204-205 | 2      | Temperature Sensor 3: NAND Flash Temperature            |  |  |

| 206-207 | 2      | Temperature Sensor 4                                    |  |  |

| 208-209 | 2      | Temperature Sensor 5                                    |  |  |

| 210-211 | 2      | Temperature Sensor 6                                    |  |  |

| 212-213 | 2      | Temperature Sensor 7                                    |  |  |

| 214-215 | 2      | Temperature Sensor 8                                    |  |  |

| 216-511 | 296    | Reserved                                                |  |  |

Note: Temperature display of the Temperature Sensor from 1 to 8 (corresponding bytes from 200 to 215) is not supported if the return value is 0h.

# Apacer

Table 8-5 SMART (C0h)

| Byte    | Length | Description                 |  |  |  |

|---------|--------|-----------------------------|--|--|--|

| 0-255   | 256    | Reserved                    |  |  |  |

| 256-257 | 2      | SSD Protect Mode            |  |  |  |

| 258-261 | 4      | Host Read UNC Count         |  |  |  |

| 262-265 | 4      | Reserved                    |  |  |  |

| 266-269 | 4      | CRC Error Count             |  |  |  |

| 270-273 | 4      | Total Early Bad Block Count |  |  |  |

| 274-277 | 4      | Total Later Bad Block Count |  |  |  |

| 278-281 | 4      | Max Erase Count             |  |  |  |

| 282-285 | 4      | Average Erase Count         |  |  |  |

| 286-289 | 4      | Program Fail Count          |  |  |  |

| 290-293 | 4      | Erase Fail Count            |  |  |  |

| 294-301 | 8      | Flash Write Sector          |  |  |  |

| 302-305 | 4      | Total Spare Block           |  |  |  |

| 306-309 | 4      | Current Spare Block         |  |  |  |

| 310-313 | 4      | Read Retry Count            |  |  |  |

| 314-511 | 210    | Reserved                    |  |  |  |

## 9. Electrical Specifications

## 9.1 Operating Voltage

Table 9-1 lists the supply voltage for PV220-M280.

**Table 9-1 Operating Range**

| Item           | Range     |

|----------------|-----------|

| Supply Voltage | 3.3V ± 5% |

## 9.2 Power Consumption

Table 9-2 lists the power consumption for PV220-M280.

**Table 9-2 Power Consumption**

| Capacity<br>Mode | Unit | 120 GB | 240 GB | 480 GB | 960 GB | 1920 GB |

|------------------|------|--------|--------|--------|--------|---------|

| Active (Max.)    | mA   | 785    | 1,115  | 1,185  | 1,210  | 1,235   |

| ldle             | IIIA | 230    | 225    | 225    | 235    | 225     |

#### Notes:

- All values are typical and may vary depending on flash configurations or host system settings.

- Power consumption is measured using CrystalDiskMark 8.0.4 with file size 1,000MB.

# **10. Mechanical Specifications**

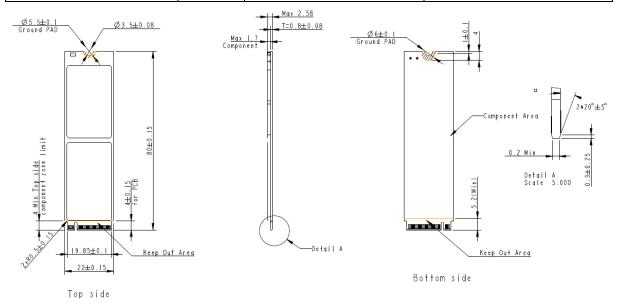

## **10.1 Single-sided Dimensions**

**Table 10-1 Physical Information**

| Parameter     | Unit   | 120 GB       | 240 GB |  |  |  |

|---------------|--------|--------------|--------|--|--|--|

| Length        |        | 80.00 ± 0.15 |        |  |  |  |

| Width         | mm     | 22.00 ± 0.15 |        |  |  |  |

| Height (Max.) |        | 2.58         |        |  |  |  |

| Weight        | g ± 5% | 6.89 7.28    |        |  |  |  |

Figure 10-1 Single-sided Dimensions

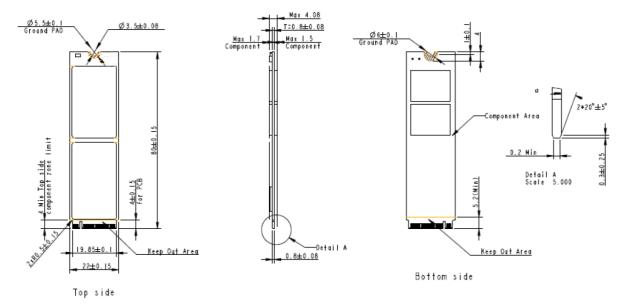

## **10.2 Double-sided Dimensions**

**Table 10-2 Physical Information**

| Parameter     | Unit   | 480 GB           | 960 GB | 1920 GB |  |  |  |

|---------------|--------|------------------|--------|---------|--|--|--|

| Length        |        | $80.00 \pm 0.15$ |        |         |  |  |  |

| Width         | mm     | 22.00 ± 0.15     |        |         |  |  |  |

| Height (Max.) |        | 4.08             |        |         |  |  |  |

| Weight        | g ± 5% | 7.23             | 7.59   | 7.7     |  |  |  |

Figure 10-2 Double-sided Dimensions

# **11. Product Ordering Information**

## **11.1 Product Code Designations**

Apacer's PV220-M280 SSD is available in different configurations and densities. See the chart below for a comprehensive list of options for the PV220-M280 series devices.

| Codo | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Code | В | 9 | 2 |   | 2 | 2 | 5 | Χ | Χ | Χ  |    | Χ  | Χ  | Χ  | Χ  | Χ  |

| Code 1-3<br>(Product Line & Form Factor) | PCIe M.2 2280                                                           |

|------------------------------------------|-------------------------------------------------------------------------|

| Code 5-6<br>(Model/Solution)             | PV220                                                                   |

| Code 7-8<br>(Product Capacity)           | 5H: 120GB<br>5J: 240GB<br>5K: 480GB<br>5L: 960GB<br>5M: 1920GB          |

| Code 9<br>(Flash Type & Product Temp)    | G: 3D TLC standard temperature<br>H: 3D TLC wide temperature            |

| Code 10<br>(Product Spec)                | V: Single-sided M key with graphene U: Double-sided M key with graphene |

| Code 12-14<br>(Version Number)           | Random numbers generated by system                                      |

| Code 15-16<br>(Firmware Version)         | 57: Thermal Sensor 120GB<br>58: Thermal Sensor 240GB-1920GB             |

## Apacer

## **11.2 Valid Combinations**

The following table lists the available models of the PV220-M280 series which are in mass production or will be in mass production. Consult your Apacer sales representative to confirm availability of valid combinations and to determine availability of new combinations.

| Capacity | Standard Temperature | Wide Temperature |

|----------|----------------------|------------------|

| 120GB    | B92.225HGV.00457     | B92.225HHV.00557 |

| 240GB    | B92.225JGV.00258     | B92.225JHV.00258 |

| 480GB    | B92.225KGU.00458     | B92.225KHU.00658 |

| 960GB    | B92.225LGU.00458     | B92.225LHU.00758 |

| 1920GB   | B92.225MGU.00458     | B92.225MHU.00658 |

# Apacer

# **Revision History**

| Revision | Description                                                                                                        | Date      |

|----------|--------------------------------------------------------------------------------------------------------------------|-----------|

| 1.0      | Initial release                                                                                                    | 4/19/2022 |

| 1.1      | - Updated endurance rating and warranty period at Endurance on<br>Specifications Overview page and 4.6 Endurance   | 8/18/2022 |

|          | - Updated pin description for Table 3-1 Pin Assignments                                                            |           |

|          | - Added 120GB and wide temp support                                                                                |           |

| 1.2      | - Updated Performance, Endurance and Power Consumption on Specifications Overview page and Tables 4-2, 4-4 and 9-2 | 9/29/2022 |

|          | - Updated 11. Product Ordering Information                                                                         |           |

| 4.0      | - Added rear view of the product to the cover page                                                                 | 0/00/0000 |

| 1.3      | - Added Sidefill support                                                                                           | 9/26/2023 |

|          | - Removed the references to "S3" and "D5" from Form factor on Specifications Overview page                         |           |

| 1.4      | - Updated Performance and Power Consumption on Specifications<br>Overview page and Table 4-2 and 9-2               | 1/11/2024 |

|          | - Removed the Write Zeroes command from Table 8-3                                                                  |           |

|          | - Updated 11. Product Ordering Information due to firmware change                                                  |           |

## **Global Presence**

### Taiwan (Headquarters)

Apacer Technology Inc.

1F., No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City 236, Taiwan R.O.C.

Tel: 886-2-2267-8000 Fax: 886-2-2267-2261 amtsales@apacer.com

### Japan

**Apacer Technology Corp.**

6F, Daiyontamachi Bldg., 2-17-12, Shibaura, Minato-Ku, Tokyo, 108-0023, Japan

Tel: 81-3-5419-2668 Fax: 81-3-5419-0018 jpservices@apacer.com

#### China

Apacer Electronic (Shanghai) Co., Ltd

Room D, 22/FL, No.2, Lane 600, JieyunPlaza, Tianshan RD, Shanghai, 200051, China

Tel: 86-21-6228-9939 Fax: 86-21-6228-9936 sales@apacer.com.cn

#### U.S.A.

Apacer Memory America, Inc.

46732 Lakeview Blvd., Fremont, CA 94538

Tel: 1-408-518-8699 Fax: 1-510-249-9551 sa@apacerus.com

#### **Europe**

Apacer Technology B.V.

Science Park Eindhoven 5051 5692 EB Son, The Netherlands

Tel: 31-40-267-0000 Fax: 31-40-290-0686 sales@apacer.nl

#### India

Apacer Technologies Pvt Ltd,

1874, South End C Cross, 9<sup>th</sup> Block Jayanagar, Bangalore-560069, India

Tel: 91-80-4152-9061/62 Fax: 91-80-4170-0215 sales\_india@apacer.com