# RoHS Compliant Micro SDHC Card

SPI Mode Appendix

March 8<sup>th</sup>, 2013

Version 1.0

Apacer Technology Inc.

4<sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1, Xizhi, New Taipei City, Taiwan 221

Tel: +886-2-2698-2888

Fax: +886-2-2698-2889

www.apacer.com

#### **Table of Contents**

| SPI Bus Timing Diagram2                                     |  |

|-------------------------------------------------------------|--|

| Command & Response2                                         |  |

| Host Command to Card Response – Card is ready2              |  |

| Host Command to Card Response – Card is busy2               |  |

| Card Response to Host Command3                              |  |

| Data Read3                                                  |  |

| Timing of Single Block Read Operation3                      |  |

| Stop Transmission Timing of Multiple Block Read Operation   |  |

| Reading the CSD or CID Register4                            |  |

| Data Write4                                                 |  |

| Timing of Multiple Block Write Operation4                   |  |

| Stop Transmission Timing of Multiple Block Write Operation5 |  |

| Timing Values5                                              |  |

| SPI Electrical Interface6                                   |  |

| SPI Bus Operation Conditions6                               |  |

| Bus Timing6                                                 |  |

## **SPI Bus Timing Diagram**

Before looking at the diagrams, please keep in mind that all timing diagrams are following the schematics and the abbreviations below.

| Н          | Signal is high (logical "1") |

|------------|------------------------------|

| L          | Signal is low (logical "0")  |

| Х          | Don't' care/ignore           |

| Z          | High impedance state (->=1)  |

| *          | Repeater                     |

| Busy       | Busy token                   |

| Command    | Command token                |

| Response   | Response token               |

| Data block | Data token                   |

## **Command & Response**

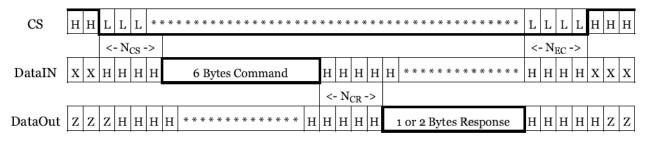

#### Host Command to Card Response - Card is ready

The following timing diagram describes the basic command response (no data) SPI transaction.

## Host Command to Card Response – Card is busy

The following timing diagram describes the command-response transaction with the R1b response (for example, SET\_WRITE\_PROT and ERASE). When the card is signaling busy, the host may de-select it (by raising the CS) at any time. The card will release the DataOut line one clock after the CS goes high. To check if the card is still busy, it needs to be re-selected by asserting (set to low) the CS signal. The card will resume busy signal (pulling DataOut low) one clock after the falling edge of CS.

| CS      | L | L | L | L | L | * * | * * | * 1 | * * 1 | * * * | *   | * * | * * | * * * | * * | * * 1 | * * * | * : | * * | * * | * * * | * * | * * | * * | * * | * * | * * | * * | * * * | * * | * * | * * | * | * | L | L | н     | н | н | 1 |

|---------|---|---|---|---|---|-----|-----|-----|-------|-------|-----|-----|-----|-------|-----|-------|-------|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|---|---|---|---|-------|---|---|---|

|         |   | _ |   |   |   |     |     |     |       |       |     |     |     |       |     |       | _     | 1   | -   |     |       | _   |     |     |     |     |     |     |       |     |     | -   | + | _ |   |   | -<br> |   | - | 1 |

| DataIN  | н | н | н | Н | Н | Н   | * * | * * | * * 1 | * * * | * * | * * | * * | * * * | * * | * * : | * H   | ł   | Н   | Н   | Н     |     | 6   | В   | yte | s ( | Cor | nr  | nar   | nd  |     | ŀ   | 1 | Н | Н | Н | х     | Х | Х |   |

|         |   |   |   |   |   |     |     |     |       |       |     |     |     |       |     |       | <     | - 1 | NR  | c - | .>    |     |     |     |     |     |     |     |       |     |     |     |   |   |   |   |       |   |   |   |

| DataOut | н | н | н | н | н |     | 1   | or  | 2     | Byte  | es  | Re  | esp | on    | se  |       | Н     | ł   | н   | Н   | н     | *   | * * | * * | * * | * * | * * | * * | * * : | * * | * * | F   | 1 | н | н | Н | н     | z | z |   |

## **Card Response to Host Command**

The following diagram describes timing between card response to new host command.

| CS      | L | L | L | L | L | * * | * * * | * * | * * * | * *  | * 1 | * * | * * | * * | * * | * * 1 | * * * | * * | *              | *    | * * | * * * * | *   | * *  | * * | *  | * * | * * | * ' | * * 1 | * * | * * | * | L | L | ŀ | 1   | Η | н |

|---------|---|---|---|---|---|-----|-------|-----|-------|------|-----|-----|-----|-----|-----|-------|-------|-----|----------------|------|-----|---------|-----|------|-----|----|-----|-----|-----|-------|-----|-----|---|---|---|---|-----|---|---|

| DatalN  | н | н | н | н | н | н   | * *   | * * | * * 1 | * *  | * : | * * | * * | * * | * * | * * : | * H   | F   | 1              | 1    | н   | (       | 6 E | Byte | es  | Сс | m   | ma  | ind | 1     | ٦   | н   | н | н | н | > |     | x | x |

|         |   |   |   |   |   |     |       |     |       |      |     |     |     |     |     |       | <     | - N | N <sub>R</sub> | ; -: | >   |         |     |      |     |    |     |     |     |       |     |     |   |   |   |   |     | • | - |

| DataOut | н | Н | н | н | н |     | 1     | or  | 21    | 3yte | s   | Re  | sp  | on  | se  |       | н     | F   | 1              | ł    | Н   | * * *   | *   | * *  | * * | *  | * * | * * | * 1 | * * 1 | *   | н   | Н | н | н | F | 1 2 | z | z |

# **Data Read**

## **Timing of Single Block Read Operation**

The following timing diagram describes all single-block read operations with the exception of SEND\_CSD and SEND\_CID commands.

| CS      | Н | L | L | L   | * * | ***  | * * * | ***     | * * * | * * | * * | * * | * * | * * * * * * * * * | * * : | ₹ * | * *   | * * | * * * | * * * * | L  | L              | L  | НH | н  | Н |

|---------|---|---|---|-----|-----|------|-------|---------|-------|-----|-----|-----|-----|-------------------|-------|-----|-------|-----|-------|---------|----|----------------|----|----|----|---|

|         |   | ÷ | N | cs- | ý   |      |       |         |       |     |     |     |     |                   |       |     |       |     |       |         | <- | N <sub>E</sub> | -> |    |    |   |

| DataIN  | x | Н | Н | Н   | н   | Read | l Co  | mman    | d H   | Н   | Н   | Н   | Н   | * * * * * * * *   | * * * | *** | • * * | ۰*  | * * * | * * * * | н  | Н              | Н  | хx | x  | х |

|         |   |   |   |     |     |      |       |         | <     | - N | CR  | ->  |     |                   | <-    | N   | AC -  | ý   |       |         |    |                |    |    |    |   |

| DataOut | z | Z | Н | Н   | Н   | н *  | * * * | * * * * | * Н   | Н   | Н   | Н   | С   | ard Response      | н     | н   | Н     | н   | Data  | 1 Block | Н  | Н              | Н  | ΗZ | zz | Z |

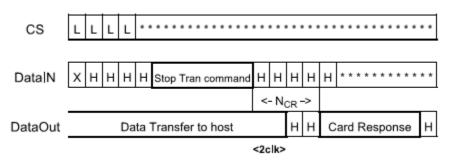

## Stop Transmission Timing of Multiple Block Read Operation

The following table describes Stop Transmission operation in case of Multiple Block Read.

Clock cycle between read data blocks are defined by NAC (not shown in the following diagram).

To avoid conflict between CMD12 response and next data block, timing of CMD12 should be controlled as follows.

1. SPI host should issue CMD12 at the timing that end bit of CMD12 and end bit of data block is overlapped.

#### Micro SDHC SPI Mode Brief

2. If 1. is not possible, SPI host should wait to receive a token (Start Block Token or Data Error Token), and then issue CMD12 after one clock from the token.

After the last block is read in case of 2., the host receives Data Error Token by out of range error. However, the data block before Data Error Token can be considered as valid if it is received successfully.

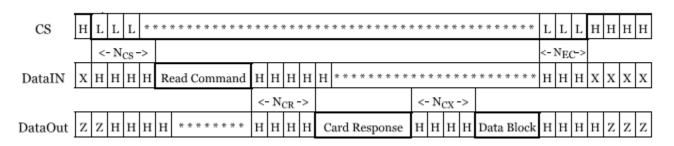

#### Reading the CSD or CID Register

The following timing diagram describes the SEND\_CSD and SEND\_CID command bus transactions. The timeout values for the response and the data block are  $N_{CR}$  and  $N_{CX}$  respectively. (Since the NAC is still unknown).

## **Data Write**

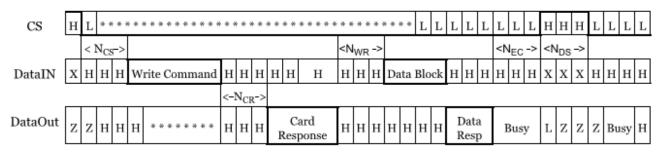

#### **Timing of Multiple Block Write Operation**

The host may de-select a card (by raising the CS) at any time during the card busy period (refer to the given timing diagram). The card will release the DataOut line one clock after the CS goes high. To check if the card is still busy, it needs to be re-selected by asserting (set to low) the CS signal. The card will resume busy signal (pulling DataOut low) one clock after the falling edge of CS.

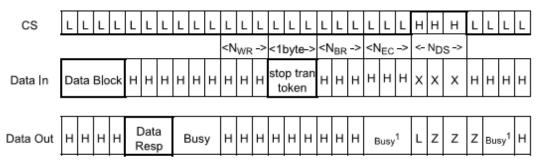

#### Stop Transmission Timing of Multiple Block Write Operation

The following figure describes stop transmission operation in multiple block write transfer. Error occurrence after the last data response token is indicated in the response of the next command.

<sup>(1)</sup> The Busy may appear within NBR clocks after the Stop Tran Token. If there is no Busy signal, the host may continue to the next command.

## **Timing Values**

All timing values are defined in the following table. The host shall keep the clock running for at least  $N_{CR}$  clock cycles after receiving the card response. This restriction applies to both command and data response tokens.

| Parameter       | Min. | Max.             | Unit           |

|-----------------|------|------------------|----------------|

| N <sub>CS</sub> | 0    | -                | 8 clock cycles |

| N <sub>CR</sub> | 1    | 8                | 8 clock cycles |

| N <sub>RC</sub> | 1    | -                | 8 clock cycles |

| N <sub>AC</sub> | 1    | spec. in the CSD | 8 clock cycles |

| N <sub>WR</sub> | 1    | -                | 8 clock cycles |

| N <sub>EC</sub> | 0    | -                | 8 clock cycles |

| N <sub>DS</sub> | 0    | -                | 8 clock cycles |

| N <sub>BR</sub> | 0    | 1                | 8 clock cycles |

| N <sub>CX</sub> | 0    | 8                | 8 clock cycles |

Notes for  $N_{AC}$ : the maximum read access time for a standard capacity SD memory card shall be calculated by host as follows

$N_{AC}$  (max) = 100 ((TAAC\*fpp)+(100\*NSAC));

fpp is the interface clock rate and TAAC & NSAC are given in the CSD (Chapter 5.3).

n the case of a high capacity SD memory card, a fixed value (100 ms) shall be used for the maximum read access time. Details of read, write and erase timeout are described in section 4.6.2 of SD card Physical Layer Specifications (ver. 3.00).

## **SPI Electrical Interface**

The electrical interface is identical to SD mode with the exception of the programmable card output drivers option, which is not supported in SPI mode.

# **SPI Bus Operation Conditions**

Bus operating conditions are identical to SD mode.

## **Bus Timing**

Bus timing is identical to SD mode. The timing of the CS signal is the same as any other card input.

# **Revision History**

| Revision | Description      | Date       |

|----------|------------------|------------|

| 1.0      | Official release | 03/08/2013 |

# **Global Presence**

| Taiwan (Headquarters) | Apacer Technology Inc.<br>4 <sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1<br>Xizhi, New Taipei City<br>Taiwan 221<br>R.O.C.<br>Tel: +886-2-2698-2888<br>Fax: +886-2-2698-2889<br>amtsales@apacer.com |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U.S.A.                | Apacer Memory America, Inc.<br>386 Fairview Way, Suite102,<br>Milpitas, CA 95035<br>Tel: 1-408-518-8699<br>Fax: 1-408-935-9611<br><u>sa@apacerus.com</u>                                            |

| Japan                 | Apacer Technology Corp.<br>5F, Matsura Bldg., Shiba, Minato-Ku<br>Tokyo, 105-0014, Japan<br>Tel: 81-3-5419-2668<br>Fax: 81-3-5419-0018<br>jpservices@apacer.com                                     |

| Europe                | Apacer Technology B.V.<br>Science Park Eindhoven 5051 5692 EB Son,<br>The Netherlands<br>Tel: 31-40-267-0000<br>Fax: 31-40-267-0000#6199<br>sales@apacer.nl                                         |

| China                 | Apacer Electronic (Shanghai) Co., Ltd<br>1301, No.251,Xiaomuqiao Road, Shanghai,<br>200032, China<br>Tel: 86-21-5529-0222<br>Fax: 86-21-5206-6939<br>sales@apacer.com.cn                            |

| India                 | Apacer Technologies Pvt Ltd,<br># 535, 1st Floor, 8th cross, JP Nagar 3rd Phase,<br>Bangalore – 560078, India<br>Tel: 91-80-4152-9061<br>sales india@apacer.com                                     |